Projects

Check out my projects below.

Hybrid Dynamical System Modeling and Inference via Machine Learning

A unified ML framework—Event-Automata + Physics-Embedded Neural ODEs + Neural Substitute Solver—for accurate, real-time inference of hybrid (continuous–discrete) dynamics with reliable Sim-to-Real transfer to edge hardware.

Design and Control of High-Frequency DC–DC Converters

From multi-DOF modulation and universal phase-shift control to device-aware electro-thermal modeling and CDT-MPC, this project delivers efficient, soft-switching, and control-ready designs for DAB/MMAB at 50–400 kHz+.

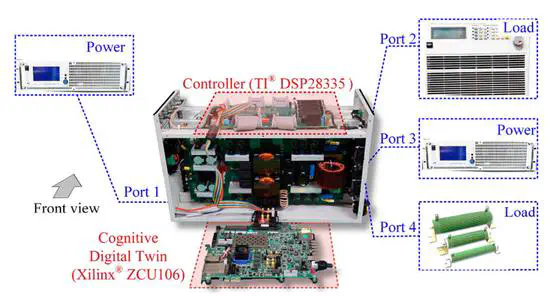

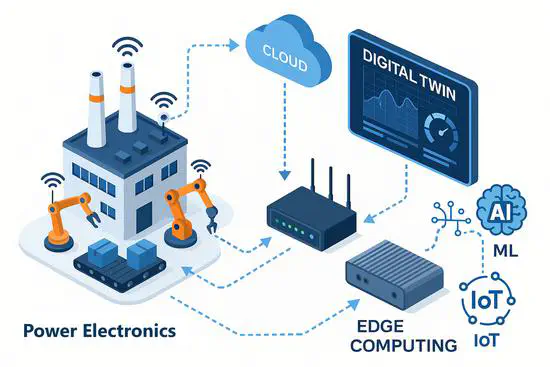

Edge Digital Twins for Power Electronics

Sim-to-Real Edge Digital Twins that fuse event-aware physics with neural operators for sub-microsecond inference, online parameter self-calibration, and control integration on FPGA/MPSoC.

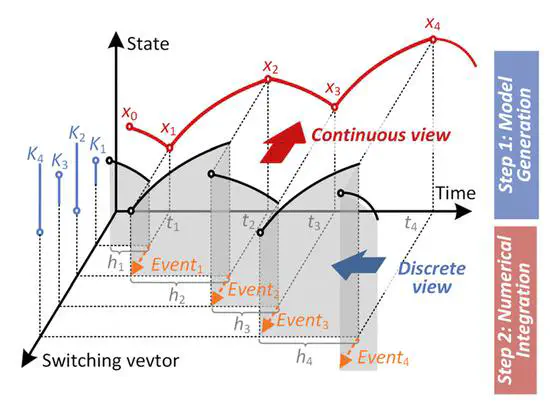

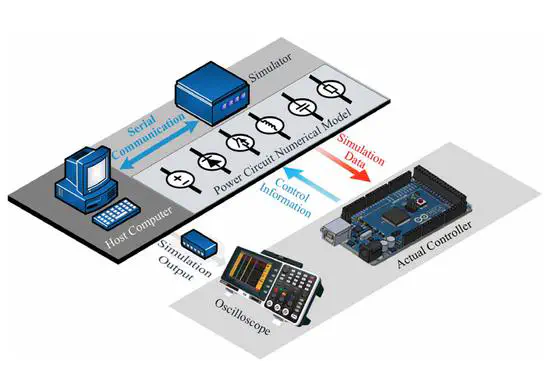

Event-Driven Efficient Simulation of Hybrid Dynamical Systems

Event-driven HIL simulation that replaces tiny fixed steps with switching-aware sampling and variable-order solvers (SCED/DHT, VTR-CHIL, DAT/SEO), enabling high-frequency, large-scale power electronics on commodity CPUs/MPSoCs.

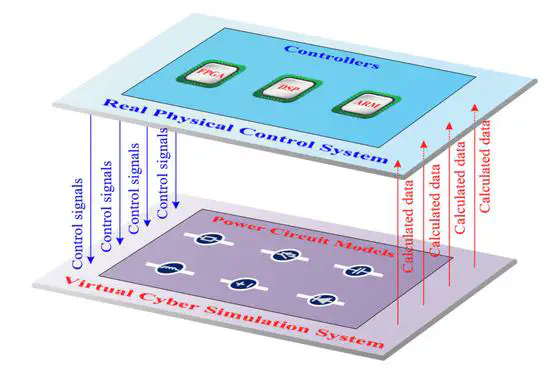

Large-Scale Cyber-Physical System Co-Simulation

Event-axis, synchronization-aware co-simulation that scales CHIL/PCCO from kW MMCs to MW-level converters by key-frame prediction, event-driven data rematching, and hybrid CPU–FPGA execution—boosting fidelity and easing real-time constraints.

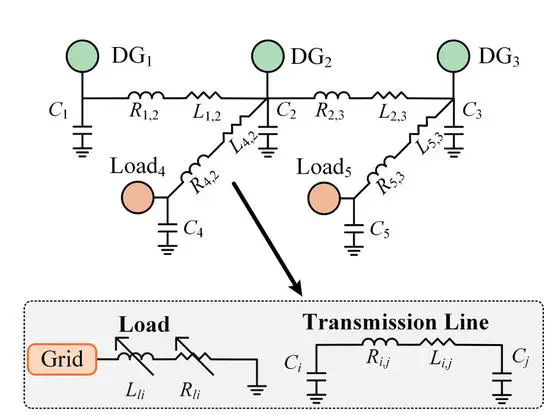

SNA: A Network-Aware Framework for Decentralized Inverter-Based Voltage Control

Network-aware multi-agent RL that scales decentralized secondary voltage control by truncating critics to κ-hop neighborhoods with provable approximation guarantees; validated up to 114 DGs.

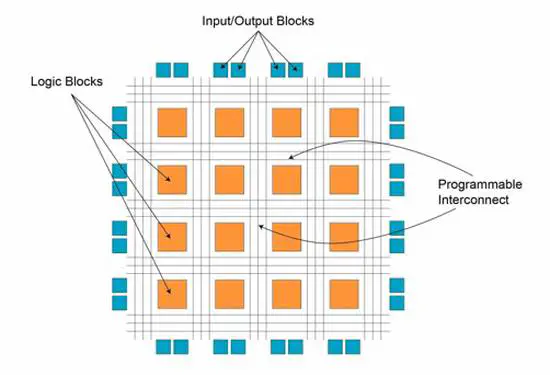

Sub-Microsecond Real-Time FPGA Numerical Solver

Deterministic sub-µs FPGA solvers (12.5–75 ns) combining semi-implicit leapfrog, topology-aware partitioning, and IMEX techniques for stability, low memory, and controller-accurate HIL.