Biography

Jialin Zheng is a Research Scientist at Princeton University and was previously a Postdoctoral Research Associate at Purdue University. He received his Ph.D. in Electrical Engineering from Tsinghua University.

His research focuses on AI-driven design and control of intelligent circuits and complex networked systems, spanning applications from integrated microwave communication to megawatt-scale power conversion and transfer. He develops advanced digital methodologies to enable scalable, high-performance circuit and integrated infrastructures across both information and power domains.

- Edge Computing

- Machine Learning

- Power Electronics

- Energy Systems

PhD in Electrical Engineering, 2024

Tsinghua University

BEng in Electrical Engineering, 2019

Beijing Jiaotong University

News

2026

- Mar-23-2026,Invited talk at Cornell AI for Sustainability (AI4S) Seminar Series: “Empowering the Grid Edge: Real-Time Embedded AI on Power Electronics Converters”.

- 18-Feb-2026,Our paper “Discovering Unknown Inverter Governing Equations via Physics-Informed Sparse Machine Learning” is subbmitted to arxiv.

2025

- 04-Jun-2024,Our paper “FPGA-based Real-Time X-in-the-loop Simulation Testbench for Dynamic Wireless Power Transfer System with Stochastic and Nonlinear Inductance” is accepted by IEEE Transactions on Industrial Electronics.

2024

- 04-Jun-2024,Our paper “FPGA-based Real-Time X-in-the-loop Simulation Testbench for Dynamic Wireless Power Transfer System with Stochastic and Nonlinear Inductance” is accepted by IEEE Transactions on Transportation Electrification.

Research Goal

My research focuses on AI-enabled design and control of intelligent circuits and complex networked systems, bridging integrated microwave communication and large-scale power conversion through advanced digital methodologies.

Projects

Check out my projects below.

Hybrid Dynamical System Modeling and Inference via Machine Learning

A unified ML framework—Event-Automata + Physics-Embedded Neural ODEs + Neural Substitute Solver—for accurate, real-time inference of hybrid (continuous–discrete) dynamics with reliable Sim-to-Real transfer to edge hardware.

Design and Control of High-Frequency DC–DC Converters

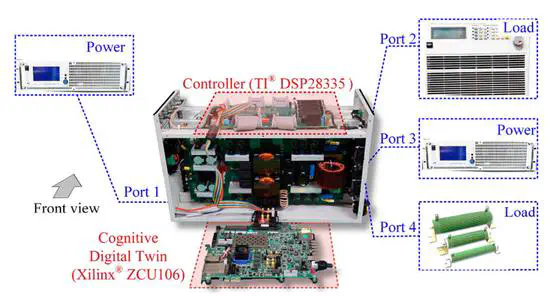

From multi-DOF modulation and universal phase-shift control to device-aware electro-thermal modeling and CDT-MPC, this project delivers efficient, soft-switching, and control-ready designs for DAB/MMAB at 50–400 kHz+.

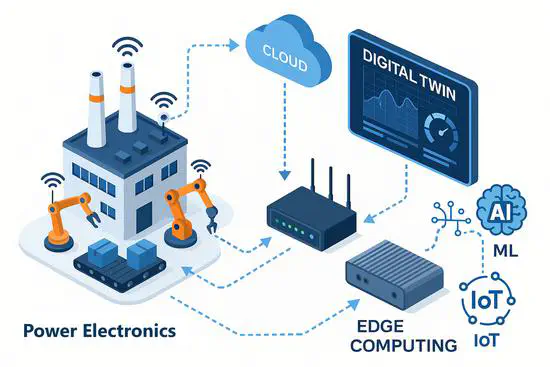

Edge Digital Twins for Power Electronics

Sim-to-Real Edge Digital Twins that fuse event-aware physics with neural operators for sub-microsecond inference, online parameter self-calibration, and control integration on FPGA/MPSoC.

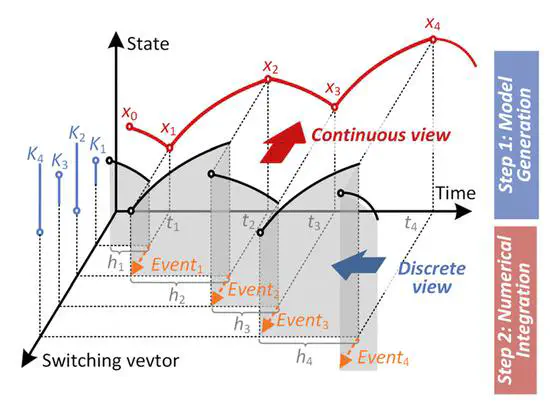

Event-Driven Efficient Simulation of Hybrid Dynamical Systems

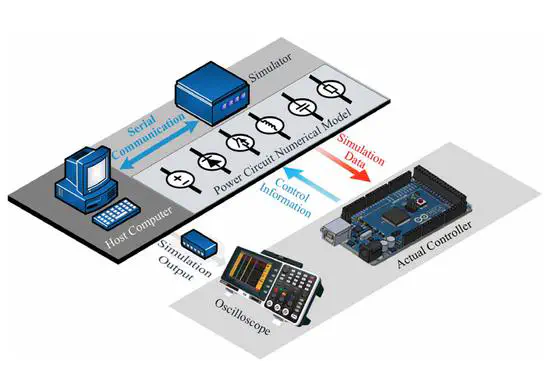

Event-driven HIL simulation that replaces tiny fixed steps with switching-aware sampling and variable-order solvers (SCED/DHT, VTR-CHIL, DAT/SEO), enabling high-frequency, large-scale power electronics on commodity CPUs/MPSoCs.

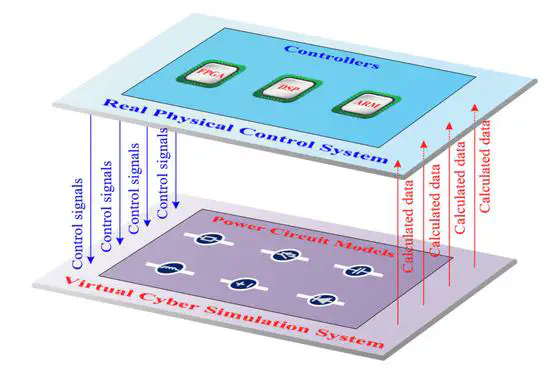

Large-Scale Cyber-Physical System Co-Simulation

Event-axis, synchronization-aware co-simulation that scales CHIL/PCCO from kW MMCs to MW-level converters by key-frame prediction, event-driven data rematching, and hybrid CPU–FPGA execution—boosting fidelity and easing real-time constraints.

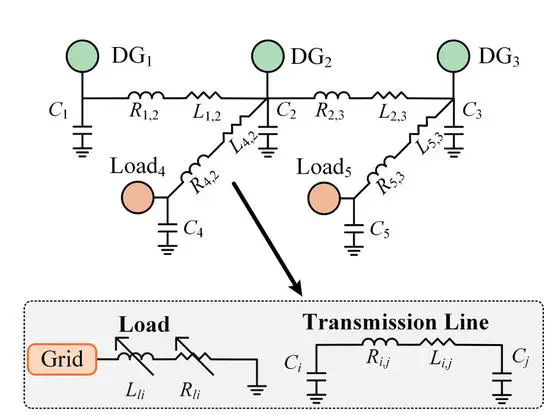

SNA: A Network-Aware Framework for Decentralized Inverter-Based Voltage Control

Network-aware multi-agent RL that scales decentralized secondary voltage control by truncating critics to κ-hop neighborhoods with provable approximation guarantees; validated up to 114 DGs.

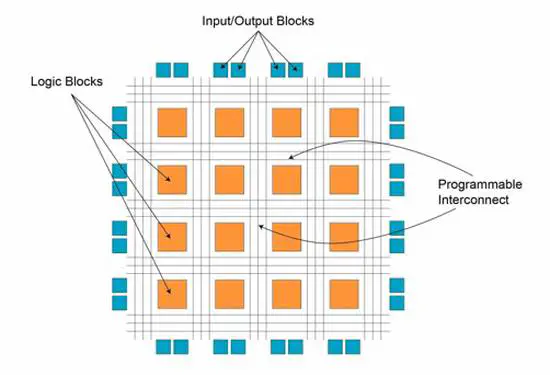

Sub-Microsecond Real-Time FPGA Numerical Solver

Deterministic sub-µs FPGA solvers (12.5–75 ns) combining semi-implicit leapfrog, topology-aware partitioning, and IMEX techniques for stability, low memory, and controller-accurate HIL.

Research Tags

Contact

Feel free to reach out for collaboration, inquiries, or feedback. Leave your name, email, and a short message—I usually reply within 2–3 business days. Your information is used solely for communication.

- jialinzheng@ieee.org

- +1 765-767-0550

- B 216, Engineering Quadrangle, Princeton, NJ 08540

- B 217/219, Engineering Quadrangle, Princeton, NJ 08540

-

Monday 10:00 to 13:00

Wednesday 09:00 to 10:00 - Book an appointment